# Self-Assembled Metallic Nanowire-Based Vertical Organic Field-Effect Transistor

Ariel J. Ben-Sasson,<sup>†</sup> Daniel Azulai,<sup>‡</sup> Hagit Gilon,<sup>‡</sup> Antonio Facchetti,<sup>§</sup> Gil Markovich,<sup>\*,‡</sup> and Nir Tessler<sup>\*,†</sup>

<sup>†</sup>Sara and Moshe Zisapel Nano-Electronics Center, Department of Electrical Engineering, Technion–Israel Institute of Technology, Haifa 3200, Israel

<sup>‡</sup>School of Chemistry, Raymond and Beverly Sackler Faculty of Exact Sciences, Tel Aviv University, Tel Aviv 69978, Israel <sup>§</sup>Polyera Corporation, 8045 Lamon Avenue, Skokie, Illinois 60077, United States

**Supporting Information**

**ABSTRACT:** We report on in situ, self-assembly, solution-processing of metallic (Au/Ag) nanowire-based transparent electrodes integrated to vertical organic field-effect transistors (VOFETs). In the VOFET architecture, the nanowires' microstructure facilitates current modulation by the gate across the otherwise shielding sandwiched source electrode. We show N-type VOFETs operation with on/off ratio ~1 × 10<sup>5</sup> and high current density (>1 mA cm<sup>-2</sup> at  $V_{DS} = 5$  V). The integration of the device design and the transparent electrode deposition methods offers a potential route for all-solution processing-based, large-area, high-efficiency organic electronics.

KEYWORDS: nanowires, self-assembly, vertical FETs, organic electronics, transparent electrodes

C olution-processed materials for optoelectronics and organic O electronics attract great interest because of their compatibility with low-cost and large-area manufacture processes.<sup>1</sup> These merits encourage research of solution-processed functional materials that enable new lighting, display, energy harvesting, sensing, and logic applications.<sup>2-6</sup> Although there is a wide selection of such substrates, insulators, semiconductors, and conductors, solution-processable, flexible, transparent eElectrodes (TEs) still struggle to reach the industrial figures of merit of transparent conductive oxides.<sup>7</sup> Numerous optoelectronic devices require TEs; such devices commonly feature a vertical architecture in which the photoactive material is sandwiched between two conductive layers, as with the case of standard light-emitting diodes (LEDs) and solar cells. But the functionality of nonoptical electronic devices that are characterized by vertical architecture is also based on TEs. Two main groups of such devices are the solid state triodes<sup>8</sup> (also referred to as space-charge-limited transistors<sup>8,9</sup>) and the more recently developed vertical fieldeffect transistors (VFETs).10-16

A key feature in the VFET is that its sandwiched source electrode would be transparent to DC electric fields so that the gate could affect the channel region. Transparency to visible light could be a bonus in some applications but it is not a must. When one is interested in extending the transparency to frequencies well below the optical spectrum or even to DC electric fields, only structured films seem to be a promising platform. These include graphene and metallic grated films, or solution-deposited carbon nanotubes (CNT) and metallic Nano-Wires (NWs) films.<sup>12,13,17</sup> CNT films tend to suffer

from relatively high sheet resistance and due to their deposition technique also tend to form high surface roughness. Metallic NWs proved to be attractive because of their low sheet resistance,<sup>18</sup> and it has been shown that they can be implemented using a variety of metals (e.g., Cu, Ag, Au, etc.), size scales, and deposition processes.<sup>19–21</sup> However, such metallic NWs films would typically also suffer from surface roughness that may make them impractical as electrodes for ~100 nm scale thick devices. We show that using a controlled synthesis of Au NWs may turn this technology one of the enabling technologies for VFETs.

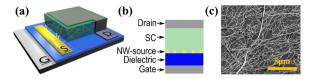

To establish a better understanding of design constraints and to explain the need for nanostructured low-roughness transparent electrode, we first describe the VFET architecture and the physics that governs its operation. The 3D illustration of the vertical FET architecture is shown in Figure 1a, and its cross-section is shown in Figure 1b. The VFET consists of the following stack of layers: gate (G), gate dielectric, source electrode (S), a semiconductor, and a top drain contact (D). This architecture has the advantage for facile fabrication of ultrashort channel length devices, as the channel length is simply determined here by the semiconductor layer's thickness. However, the source electrode, which is sandwiched between the gate and the semiconductor, introduces significant shielding effects, similar to a Faraday cage. A source electrode made of high quality conductors such as metals, where the Debye

Received: August 3, 2014 Accepted: January 20, 2015 Published: January 20, 2015

# **ACS Applied Materials & Interfaces**

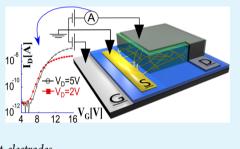

**Figure 1.** (a, b) Illustration of the Au/Ag Metallic NW-based VOFET (MN-VOFET) architecture. The metallic NW film serves as the embedded transparent electrodes between the bottom gate, gate dielectric layers, and the upper semiconductor and drain layers. (c) High-resolution scanning electron microscopy (HRSEM) of a metallic NWs film (indicated with bright color).

shielding length can be approximated to the atomic scale, may completely separate the VFET into two functional parts: a capacitor below the source, and a diode above it. To allow these parts to interact, the source electrode has to be transparent to the low-frequency or DC vertical gate electric fields. As discussed in previous works<sup>14,22–24</sup> and demonstrated both theoretically and experimentally, that nanostructured or gridlike shaped films can achieve this type of transparency. Namely, the type of VFET discussed here is the patterned electrode (source) VFET.<sup>13</sup>

As expected, the physical underpinnings of the VFET's operation differ from those of its lateral counterpart. The VFET is governed by several mechanisms, which we addressed in depth in references<sup>24</sup> and.<sup>25</sup> The very basic mechanism, which we term as the virtual contact formation, relies on a high potential-barrier between the source and the semiconductor to minimize direct source-drain currents at Off state (Schottky barrier contact). In the on state, gate electric fields diminish the Schottky barrier; they penetrate into the openings in the source electrode and induce charge injection and formation of regions saturated with mobile charge carriers, which can now flow toward the drain. With that, the source electrode film (and in microscale view the perforation regions) behaves as an ohmic contact, and is no longer considered a current limiting factor.<sup>23</sup> This charge accumulation at the openings in the source electrode (i.e., the virtual contact) is confined by the metallic source electrode perforations' "walls", hence the high significance of these regions' aspect ratio (source thickness to perforation size). In fact, this parameter is so important that any

slight change in the aspect ratio directly translates to a significant variation in the device's performance. For example, we previously demonstrated that a 5% variation in the aspect ratio resulted in an order of magnitude change in the device on/off ratio.<sup>24</sup>

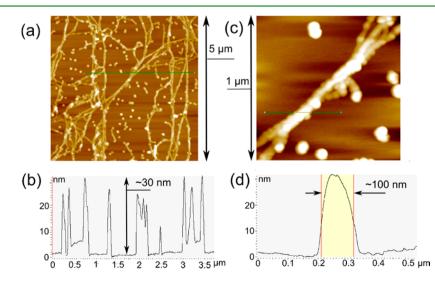

However, the effect of rough electrodes extends beyond the direct influence of the aspect ratio on the device performance. In practice it could also reduce the effective film thickness promoting high Off currents, and at the extreme, may also lead to pinholes formation between the source and the drain. Given we aim at sub 100 nm channel length (active layer thickness) devices, a fine-tuned nanostructured electrode fabrication is a necessity. We found that controlling the NWs self-assembly initiation process is the key point to achieve layer uniformity that would allow for reproducible results. Thus, instead of using protocols using borohydride as the catalytic initiator,<sup>19</sup> we followed a work reporting the synthesis of metal NWs from preprepared catalytic nanogold seeds.<sup>26</sup> This by itself was not enough and we achieved further reduction in the film roughness by lowering the NWs' surface density, using lower  $(\times 3)$  concentration solutions. The resulting film was characterized using AFM as shown in Figure 2. The maximum NWs film height is found to be below 30 nm (Figure 2a, b), a typical width of a NW bundle is about 100 nm (Figure 2c, d), and the distance between bundles is a few hundreds of nanometers. Comparing with the design rules in ref 23 and 25, the distance between the bundles corresponds to the diameter (D) of the hole in the electrode and the height corresponds to the electrode thickness (h). The aspect ratio of h/D achieved here is low enough to allow for a high on/off ratio.<sup>23,25</sup>

Following the formation of the NWs electrode on the Si/SiO<sub>2</sub> substrate (100 nm SiO<sub>2</sub> as gate insulator) we completed the VFET structure by depositing an active layer and Al top contact. The overlap between the three electrodes defines the device area that here is about  $1 \times 10^{-4}$  cm<sup>2</sup> (more details are in the Supporting Information). On the basis of the improved NWs film properties we were able to use a thin active layer as the polymer P(NDI2OD-T2) (Polyera, ActivInk N2200) that was spin coated (12 mg/mL chloroform at 4k rpm) to ~100 nm thick layer. The choice of this polymer was made due to several reasons. It can be deposited from orthogonal solutions

**Figure 2.** AFM image of the nanowires film after the second stabilization dipping step: (a)  $5 \times 5 \mu m$  image. (b) Cross-section along the line sown in a. (c)Zoom on a single NW bundle. (d) Cross-section along the line shown in c.

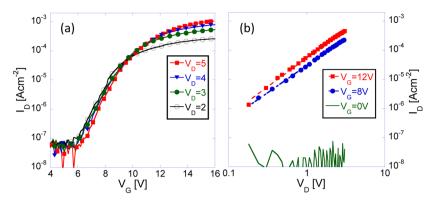

Figure 3. I-V characteristics of vertical FETs based on the N2200 polymer. (a) Transfer characteristics,  $I_D-V_G$ . (b) Output characteristics,  $I_D-V_D$ . The dashed lines in b are power-law fits.

(chloroform) to the NWs film. It is an n-type air-stable semiconductor and its LUMO level (~4 eV) should be sufficiently distanced from the NWs' work function. Examining the device transfer characteristics shown in Figure 3a, one can immediately spot several key features. The VFET turns on at about  $V_{\rm G}$  = 5.5 V and below that the current is negligible and very close to our measurement setup resolution (pA). At the vicinity of the turn-on voltage the drain bias has very little effect on the current. The suppression of the direct effect of the drain voltage also results in an on/off ratio approaching  $1 \times 10^{\circ}$ . Turn on slope is reasonable for this structure (SS = 1 V/dec) and the current saturates at approximately  $V_G = 12$  V. Figure 3b shows the output  $(I_D - V_D)$  characteristics of the VFET where for the gate bias of 8 and 12 we fitted the data to a power law function (dashed lines). The power law for gate bias of 8 and 12 was found to be 1.9 and 2, respectively. This indicates that the gate has indeed turned the source contact into an ohmic one making the current voltage characteristics space charge limited.23,25

To summarize, this work highlights the potential of using a random network of metallic NWs as the source electrode for low-cost vertical FETs. We demonstrated a process showing how judicial choice of the NWs synthesis protocol as well as the active semiconducting materials can result in high performance n-type devices featuring high on/off ratio (>1  $\times$  10<sup>4</sup>), high driving current density (1 × 10<sup>-3</sup> A cm<sup>-2</sup> at  $V_{\rm DS}$  = 5 V), and reasonable subthreshold slope (~1 V/dec). In future work, we aim to integrate NWs with intermediate diameter (~8 nm) in our devices: With much higher fill factor because of their nonbundled assembly, they retain a similar visible spectrum transparency but, at the same time, we expect them to provide a superior low-frequency electric field transparency. Thus, we strongly believe that having demonstrated solution-processed, smooth, and transparent NW electrodes constitutes a key milestone in enabling lithography-free, ultrashort channel length devices for low-cost and highly efficient organic electronics.

# ASSOCIATED CONTENT

## **Supporting Information**

Experimental section (PDF). This material is available free of charge via the Internet at http://pubs.acs.org.

#### AUTHOR INFORMATION

#### **Corresponding Authors**

\*E-mail: nir@ee.technion.ac.il.

\*E-mail: gilmar@post.tau.ac.il.

## Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

This research was supported by the Israel Science Foundation (Grant 695/10) and the Russell Berrie Nanotechnology Institute at the Technion – Israel Institute of Technology. Ariel J. Ben-Sasson is grateful to the Azrieli Foundation for the award of an Azrieli fellowship. Part of the device fabrication process was performed at the Technion's micronano fabrication unit (MNFU).

## REFERENCES

(1) Forrest, S. R. The Path to Ubiquitous and Low-Cost Organic Electronic Appliances on Plastic. *Nature* **2004**, 428, 911–918.

(2) Reineke, S.; Lindner, F.; Schwartz, G.; Seidler, N.; Walzer, K.; Lussem, B.; Leo, K. White Organic Light-Emitting Diodes with Fluorescent Tube Efficiency. *Nature* **2009**, *459*, 234–238.

(3) Sekitani, T.; Zaitsu, K.; Noguchi, Y.; Ishibe, K.; Takamiya, M.; Sakurai, T.; Someya, T. Printed Nonvolatile Memory for a Sheet-Type Communication System. *IEEE Trans. Electron Devices* **2009**, *56*, 1027–1035.

(4) Bao, Z.; Locklin, J. J. Organic Field-Effect Transistors; CRC Press: Boca Raton, FL, 2007.

(5) Wadia, C.; Alivisatos, A. P.; Kammen, D. M. Materials Availability Expands the Opportunity for Large-Scale Photovoltaics Deployment. *Environ. Sci. Technol.* **2009**, *43*, 2072–2077.

(6) Someya, T.; Kato, Y.; Sekitani, T.; Iba, S.; Noguchi, Y.; Murase, Y.; Kawaguchi, H.; Sakurai, T. Conformable, Flexible, Large-Area Networks of Pressure and Thermal Sensors with Organic Transistor Active Matrixes. *Proc. Natl. Acad. Sci. U.S.A.* **2005**, *102*, 12321–12325. (7) Barnes, T. M.; Reese, M. O.; Bergeson, J. D.; Larsen, B. A.; Blackburn, J. L.; Beard, M. C.; Bult, J.; van de Lagemaat, J. Comparing the Fundamental Physics and Device Performance of Transparent, Conductive Nanostructured Networks with Conventional Transparent Conducting Oxides. *Adv. Energy Mater.* **2012**, *2*, 353–360.

(8) Yang, Y.; Heeger, A. J. A New Architecture for Polymer Transistors. *Nature* **1994**, 372, 344–346.

(9) Yu-Chiang, C.; Chun-Yu, C.; Hsiao-Wen, Z.; Hsin-Fei, M. The Influences of Device Geometry and P-Type Doping on a Solution-Processed Polymer Space-Charge-Limited Transistor. *J. Phys. D: Appl. Phys.* **2010**, 43, 205101.

(10) Ma, L. P.; Yang, Y. Unique Architecture and Concept for High-Performance Organic Transistors. *Appl. Phys. Lett.* **2004**, *85*, 5084–5086.

(11) Globerman, O. Lateral and Vertical Organic Field Effect Transistors; Technion Israel Institute of Technology: Haifa, Israel, 2006.

(12) Liu, B.; McCarthy, M. A.; Yoon, Y.; Kim, D. Y.; Wu, Z.; So, F.; Holloway, P. H.; Reynolds, J. R.; Guo, J.; Rinzler, A. G. Carbon-

2151

## **ACS Applied Materials & Interfaces**

Nanotube-Enabled Vertical Field Effect and Light-Emitting Transistors. Adv. Mater. 2008, 20, 3605–3609.

(13) Ben-Sasson, A. J.; Avnon, E.; Ploshnik, E.; Globerman, O.; Shenhar, R.; Frey, G. L.; Tessler, N. Patterned Electrode Vertical Field Effect Transistor Fabricated Using Block Copolymer Nanotemplates. *Appl. Phys. Lett.* **2009**, *95*, 213301.

(14) McCarthy, M. A.; Liu, B.; Donoghue, E. P.; Kravchenko, I.; Kim, D. Y.; So, F.; Rinzler, A. G. Low-Voltage, Low-Power, Organic Light-Emitting Transistors for Active Matrix Displays. *Science* **2011**, *332*, 570–573.

(15) Seidel, K.; Rossi, L.; Mello, R. Q.; Hümmelgen, I. Vertical Organic Field Effect Transistor Using Sulfonated Polyaniline/ Aluminum Bilayer as Intermediate Electrode. *J. Mater. Sci: Mater. Electron* **2013**, *24*, 1052–1056.

(16) Kleemann, H.; Günther, A. A.; Leo, K.; Lüssem, B. High-Performance Vertical Organic Transistors. *Small* **2013**, *9*, 3670–3677.

(17) Lemaitre, M. G.; Donoghue, E. P.; McCarthy, M. A.; Liu, B.; Tongay, S.; Gila, B.; Kumar, P.; Singh, R. K.; Appleton, B. R.; Rinzler, A. G. Improved Transfer of Graphene for Gated Schottky-Junction, Vertical, Organic, Field-Effect Transistors. *ACS Nano* **2012**, *6*, 9095– 9102.

(18) Kumar, A.; Zhou, C. The Race to Replace Tin-Doped Indium Oxide: Which Material Will Win? ACS Nano 2010, 4, 11–14.

(19) Azulai, D.; Belenkova, T.; Gilon, H.; Barkay, Z.; Markovich, G. Transparent Metal Nanowire Thin Films Prepared in Mesostructured Templates. *Nano Lett.* **2009**, *9*, 4246–4249.

(20) van de Groep, J. V.; Spinelli, P.; Polman, A. Transparent Conducting Silver Nanowire Networks. *Nano Lett.* **2012**, *12*, 3138– 3144.

(21) Yue, Y.; Liu, P.; Zhang, Z.; Han, X.; Ma, E. Approaching the Theoretical Elastic Strain Limit in Copper Nanowires. *Nano Lett.* **2011**, *11*, 3151–3155.

(22) Chen, W.; Rinzler, A.; Guo, J. Computational Study of Graphene-Based Vertical Field Effect Transistor. J. Appl. Phys. 2013, 113, 094507.

(23) Ben-Sasson, A. J.; Tessler, N. Patterned Electrode Vertical Field Effect Transistor: Theory and Experiment. J. Appl. Phys. 2011, 110, 12.

(24) Ben-Sasson, A. J.; Tessler, N. Unraveling the Physics of Vertical Organic Field Effect Transistors through Nanoscale Engineering of a Self-Assembled Transparent Electrode. *Nano Lett.* **2012**, *12*, 4729–4733.

(25) Ben-Sasson, A. J.; Tessler, N. Patterned Electrode Vertical Ofet: Analytical Description, Switching Mechanisms, and Optimization Rules. *SPIE* **2011**, *8117*, 81170Z.

(26) Azulai, D.; Cohen, E.; Markovich, G. Seed Concentration Control of Metal Nanowire Diameter. *Nano Lett.* **2012**, *12*, 5552– 5558.